## **TFT DISPLAY SPECIFICATION**

WINSTAR Display Co.,Ltd. 華凌光電股份有限公司

WEB: <a href="https://www.winstar.com.tw">https://www.winstar.com.tw</a> E-mail: sales@winstar.com.tw

#### **SPECIFICATION**

| CUSTOMER :                |              |        |

|---------------------------|--------------|--------|

| MODULE NO.:               | WF50DTYA31   | MNG10# |

|                           | 1            |        |

|                           |              |        |

| APPROVED BY:              | 9 //r        |        |

| ( FOR CUSTOMER USE ONLY ) | (5)          |        |

|                           | PCB VERSION: | DATA:  |

| SALES BY     | APPROVED BY | CHECKED BY | PREPARED BY |

|--------------|-------------|------------|-------------|

|              |             |            | 葉虹蘭         |

| ISSUED DATE: | 2020/03/27  |            |             |

TFT Display Inspection Specification: <a href="https://www.winstar.com.tw/technology/download.html">https://www.winstar.com.tw/technology/download.html</a>

Precaution in use of TFT module: <a href="https://www.winstar.com.tw/technology/download/declaration.html">https://www.winstar.com.tw/technology/download/declaration.html</a>

MODLE NO:

| REC     | ORDS OF REV | ISION               | DOC. FIRST ISSUE                        |

|---------|-------------|---------------------|-----------------------------------------|

| VERSION | DATE        | REVISED<br>PAGE NO. | SUMMARY                                 |

| 0       | 2017/10/30  |                     | First issue                             |

| A       | 2019/02/12  |                     | Add Drive IC                            |

| В       | 2019/05/03  |                     | Add Brightness and                      |

| С       | 2020/03/27  |                     | Uniformity. TFT Interface: 4-Lanes MIPI |

## **Contents**

- 1.Module Classification Information

- 2.Summary

- 3. General Specification

- 4. Absolute Maximum Ratings

- 5. Electrical Characteristics

- 6.DC Characteristics

- 7.AC Characteristics

- 8. Waveform

- 9. Optical Characteristics

- 10.Interface

- 11.Reliability

- 12. Touch Panel Information

- 13.Contour Drawing

- 14.Other

## 1.Module Classification Information

A 3 G 0# W F 50 D T Y M N 1 1 3 7 8 9 (11) (12) 13) 2 4 (5) 6 10

| ①           | Brand: WINSTAR DISPLAY CORPORATION     |                                                                                                                            |        |          |        |       |        |                         |             |          |             |          |              |

|-------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------|----------|--------|-------|--------|-------------------------|-------------|----------|-------------|----------|--------------|

| 2           | Display Type: F→TFT Type, J→Custom TFT |                                                                                                                            |        |          |        |       |        |                         |             |          |             |          |              |

| 3           | Display Size : 5.0                     | )" TFT                                                                                                                     |        |          |        |       |        |                         |             |          |             |          |              |

| 4           | Model serials no.                      |                                                                                                                            |        |          |        |       |        |                         |             |          |             | A        |              |

| (5)         | Backlight                              | F→CCFL, W                                                                                                                  | hite   |          |        |       | Т      | $\rightarrow$ L         | ED, White   | <b>;</b> |             |          |              |

| 9           | Type:                                  | S→LED, Hig                                                                                                                 | h Lig  | ght Wh   | ite    |       | Z      | Z→N                     | ichia LED   | ), W     | hite        |          |              |

|             | LCD Polarize                           | A→Transmis                                                                                                                 | sive,  | N.T, II  | PS T   | FT    | Ç      | <b>2</b> →T             | ransmissiv  | e, S     | uper W.T,   | 12:00    | )            |

|             | Type/                                  | C→Transmis                                                                                                                 | sive,  | N. T, 6  | :00    | ,     | R      | R→Ti                    | ransmissiv  | e, S     | uper W.T,   | O-TF     | Т            |

|             | Temperature                            | F→Transmiss                                                                                                                | sive,  | N.T,12   | :00;   |       | V      | / <b>→</b> T            | ransmissiv  | e, S     | uper W.T,   | VA T     | FT           |

| 6           | range/ Gray                            | I→Transmiss                                                                                                                | ive, V | W. T, 6: | :00    |       | V      | V→T                     | Transmissi  | ve,      | Super W.T,  | IPS '    | $\Gamma F T$ |

|             | Scale Inversion                        | K→Transflec                                                                                                                | tive,  | W.T,12   | 2:00   |       | X      | ζ→Т                     | ransmissiv  | /e, V    | V.T, VA TF  | T        |              |

|             | Direction                              | L→Transmis                                                                                                                 | sive,  | W.T,12   | 2:00   |       | Y      | / <b>→</b> T            | ransmissiv  | ve, V    | V.T, IPS TI | T        |              |

|             | Direction                              | N→Transmis                                                                                                                 | sive,  | Super    | W.T,   | 6:00  | z      | Z→Tı                    | ransmissiv  | e, V     | V.T, O-TFT  | 1        |              |

|             | A: TFT LCD                             |                                                                                                                            |        |          |        |       | F      | 7 : T                   | FT+CON7     | ΓRO      | L BOAR      | D        |              |

|             | B: TFT+SCREV                           | V HOLES+CC                                                                                                                 | NTR    | OL BO    | OAR    | D     | C      | 3 : T                   | FT+ SCR     | EW       | HOLES       |          |              |

| 7           | C: TFT+ SCRE                           | W HOLES +A                                                                                                                 | /D B   | OARD     | C      | X     | H      | $\mathbf{H}:\mathbf{T}$ | FT+D/V      | BC       | OARD        |          |              |

|             | D: TFT+ SCREW                          | HOLES +A/D B                                                                                                               | OARD   | +CONT    | ROL    | BOA   | RD I   | : TF                    | T+ SCRE     | W        | HOLES +D    | /V B     | OARD         |

|             | E: TFT+ SCREV                          | W HOLES +PO                                                                                                                | OWE    | R BO     | OAR    | D     | J      | : TF                    | T+POWE      | ER E     | BD          |          |              |

|             | Resolution:                            |                                                                                                                            |        |          |        |       |        |                         |             |          |             |          |              |

|             | A 128160 B                             | 320234                                                                                                                     | 32     | 20240    | D      | 480   | 0234   | Е                       | 480272      | F        | 640480      |          |              |

| 8           | G 800480 H                             | 1024600 I                                                                                                                  | 32     | 20480    | J      | 24    | 0320   | K                       | 800600      | L        | 240400      |          |              |

| 0           | M 1024768 N                            | 128128 F                                                                                                                   | 12     | 80800    | Q      | 480   | 0800   | R                       | 640320      | S        | 480128      |          |              |

|             | T 800320 U                             | 8001280 <b>V</b>                                                                                                           | 17     | 6220     | W      | 128   | 0398   | X                       | 1024250     | Y        | 1920720     |          |              |

|             | Z 800200 2                             | 1024324 3                                                                                                                  | 720    | 01280    | 4      | 192   | 01200  | 5                       | 1366768     | 6        | 1280320     |          |              |

| 9           | D: Digital L:                          | LVDS M:M                                                                                                                   | IPI    |          |        |       |        |                         |             |          |             |          |              |

|             | Interface:                             | /                                                                                                                          |        |          |        |       |        |                         |             |          |             |          |              |

| 10          | N Without co                           | ntrol board                                                                                                                | A      | 8Bit     |        | В     |        | 16B                     | Bit         | Н        | HDMI        |          |              |

|             | I I2C Interfa                          | ce                                                                                                                         | R      | RS23     | 2      | S     | SP     | I Inte                  | erface      | U        | USB         |          |              |

|             | TS:                                    | •                                                                                                                          |        | •        |        |       |        |                         | •           |          | •           | <u>'</u> |              |

|             | N Without TS                           |                                                                                                                            | Т      | Resist   | ive t  | oucl  | pane   | el                      | C Capaci    | tive     | touch pane  | el (G-   | F-F)         |

| <u>(11)</u> | G Capacitive to                        | ve touch panel (G-G)  C1   Capacitive touch panel (G-F-F)+OCA                                                              |        |          |        |       |        | A                       |             |          |             |          |              |

|             | C2 Capacitive to                       | ouch panel (G-                                                                                                             | F-F)-  | +OCR     |        | G     | 1 C    | apac                    | itive touch | par      | nel (G-G)+  | OCA      |              |

|             | G2 Capacitive to                       | C2 Capacitive touch panel (G-F-F)+OCR G1 Capacitive touch panel (G-G)+OCA G2 Capacitive touch panel (G-G)+OCR B CTP+GG+USB |        |          |        |       |        |                         |             |          |             |          |              |

| 12          | <u> </u>                               | oberry pi                                                                                                                  |        |          |        |       | ı      |                         |             |          |             |          |              |

| 13          | Special Code                           | #:Fit in wit                                                                                                               | h RC   | )HS diı  | rectiv | ve re | gulati | ons                     |             |          |             |          |              |

|             | 1 *                                    | I                                                                                                                          |        |          |        |       |        |                         |             |          |             |          |              |

## 2.Summary

TFT 5.0" is a color active matrix thin film transistor (TFT) liquid crystal display (LCD) that uses amorphous silicon TFT as a switching device. This TFT LCD has a 4.99 (16:9) inch diagonally measured active display area with HD (720 horizontal by 1280 vertical pixel) resolution. This module is a composed of a TFT\_LCD module and follows RoHs.

WF50DTYA3MNG10#

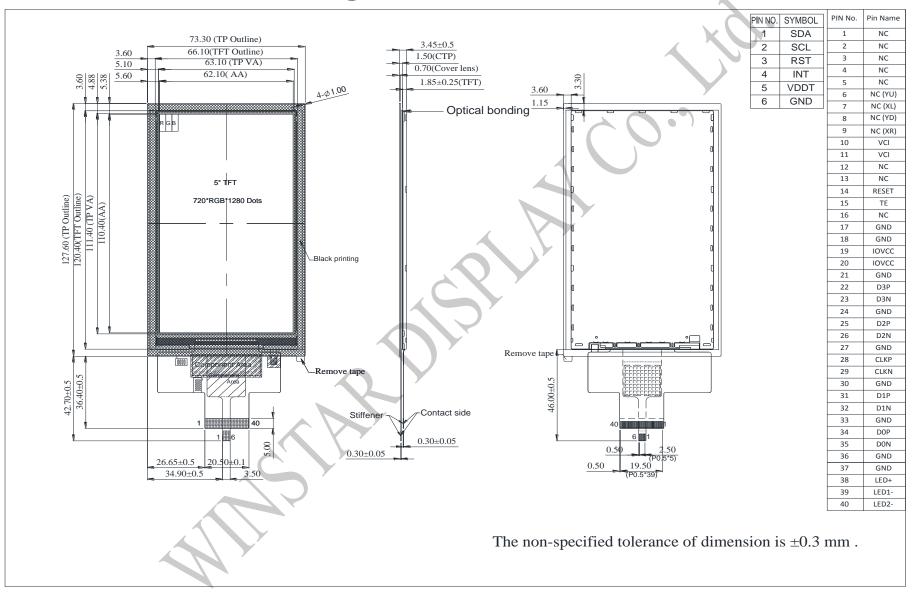

## **3.General Specifications**

| Item             | Dimension                         | Unit |

|------------------|-----------------------------------|------|

| Size             | 5.0                               | inch |

| Dot Matrix       | 720× 3(RGB) ×1280                 | dots |

| Module dimension | 73.3 (W) × 127.6 (H) ×3.45        | mm   |

| Active area      | 62.1 (W) × 110.4 (H)              | mm   |

| Dot pitch        | 0.08625(W) ×0.08625(H)            | mm   |

| LCD type         | TFT, Normally Black, Transmissive |      |

| Viewing angle    | 80/80/80/80                       |      |

| Aspect Ratio     | 16:9                              |      |

| Backlight Type   | LED ,Normally White               |      |

| TFT Drive IC     | ILI9881C or Equivalent            |      |

| TFT Interface    | 4-Lanes MIPI                      |      |

| CTP FW Version   | 0x5F                              |      |

| CTP IC           | GT928                             |      |

| With /Without TP | With CTP                          |      |

| Surface          | Glare                             |      |

<sup>\*</sup>Color tone slight changed by temperature and driving voltage.

## **4.Absolute Maximum Ratings**

| Item                  | Symbol | Min | Тур | Max | Unit                   |

|-----------------------|--------|-----|-----|-----|------------------------|

| Operating Temperature | TOP    | -20 | _   | +70 | $^{\circ}\mathbb{C}$   |

| Storage Temperature   | TST    | -30 | _   | +80 | $^{\circ}\!\mathbb{C}$ |

Note: Device is subject to be damaged permanently if stresses beyond those absolute maximum ratings listed above

1. Temp.  $\leq\!60^{\circ}\!\!\!\mathrm{C}$  , 90% RH MAX. Temp.  $>\!60^{\circ}\!\!\mathrm{C}$  , Absolute humidity shall be less than 90% RH at  $60^{\circ}\!\!\mathrm{C}$

## **5.Electrical Characteristics**

#### **5.1. Typical Operation Conditions**

| Item                            | Symbol |      | Values |      | Unit | Remark   |  |

|---------------------------------|--------|------|--------|------|------|----------|--|

| item                            | Symbol | Min. | Тур.   | Max. | Onit | Kemark   |  |

| Power supply for analog circuit | VCI    | 2.5  | 3.3    | 3.6  | V    |          |  |

| Power supply for logic circuit  | IOVCC  | 1.65 | 1.8    | 3.6  | V    |          |  |

| Supply Voltage For Touch Logic  | VDDT   | 2.8  | -      | 3.3  | V    |          |  |

| Current for Driver              | IDD    | ı    | 44     | ı    | mA   | VDD=3.3V |  |

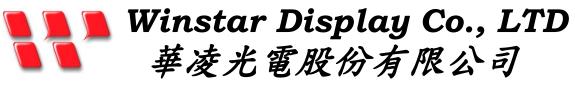

#### 5.2. Backlight Driving Conditions

| Parameter     | Symbol | Min.   | Тур. | Max. | Unit | Remark     |

|---------------|--------|--------|------|------|------|------------|

| LED current   | ILED   | -      | 40   | ı    | mA   |            |

| LED voltage   | VLED+  | 19.6   | -    | 23.8 | V    | Note 1     |

| LED Life Time |        | 30,000 | -    | -    | Hr   | Note 2,3,4 |

Note 1: There are 1 Groups LED

Note 2 : Ta = 25 °C

Note 3: Brightness to be decreased to 50% of the initial value

Note 4: The single LED lamp case

## **6.DC CHARATERISTICS**

#### 6.1. Basic Characteristics for Panel Driving

| Parameter                              | Symbol          |           | Rating  |           | Unit | Condition                | Note  |

|----------------------------------------|-----------------|-----------|---------|-----------|------|--------------------------|-------|

| 1 arameter                             | Symbol          | Min       | Min Typ |           | Ome  | Condition                | Tiote |

| Logic Low level input voltage          | VIL             | -0.3      | -       | 0.3*IOVCC | V    |                          | Note1 |

| Logic High level input voltage         | V <sub>IH</sub> | 0.7*IOVCC | -       | IOVCC     | V    | X                        | Note1 |

| Logic Low level<br>output voltage (TE) | Vol             | 0         |         | 0.2*IOVCC | V    | I <sub>OL</sub> = +1.0mA | Note1 |

| Logic High level output voltage (TE)   | Voh             | 0.8*IOVCC |         | IOVCC     | v    | Iон= -1.0mA              | Note1 |

NOTE1:

Ta = -20 to  $70^{\circ}$ C, VCI = 2.5V to 3.6V, IOVCC = 1.65V to 3.6V

#### 6.2. DSI DC Characteristics

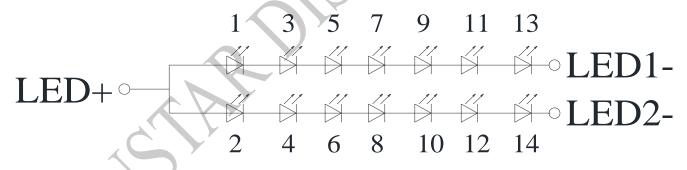

#### LP Mode

| Damamatan              | O. mahal               | Condition                   |      | Unit |      |    |

|------------------------|------------------------|-----------------------------|------|------|------|----|

| Parameter              | Symbol                 | Condition                   | Min. | Тур. | Max. |    |

| Logic 1 input voltage  | $V_{IHLPCD}$           | LP-CD                       | 450  | -    | 1350 | m∨ |

| Logic 0 input voltage  | V <sub>ILLPCD</sub>    | LP-CD                       | 0.0  | -    | 200  | m∨ |

| Logic 1 input voltage  | $V_{IHLPRX}$           | LP-RX (CLK, D0 ,D1, D2, D3) | 880  | -    | 1350 | m∨ |

| Logic 0 input voltage  | $V_{ILLPRX}$           | LP-RX (CLK, D0 ,D1, D2, D3) | 0.0  | -    | 550  | m∨ |

| Logic 0 input voltage  | V <sub>ILLPRXULP</sub> | LP-RX (CLK ULP mode)        | 0.0  | -    | 300  | m∨ |

| Logic 1 output voltage | V <sub>OHLPTX</sub>    | LP-TX (D0)                  | 1.1  | -    | 1.3  | V  |

| Logic 0 output voltage | $V_{OLLPTX}$           | LP-TX (D0)                  | -50  | -    | 50   | m∨ |

| Logic 1 input current  | I <sub>IH</sub>        | LP-CD, LP-RX                | -    | -    | 10   | uA |

| Logic 0 input current  | I <sub>IL</sub>        | LP-CD, LP-RX                | -10  | -    | -    | uA |

#### Spike/Glitch Rejection

| Spike/Glitch Rejection – DSI |        |                               |     |     |      |  |  |  |

|------------------------------|--------|-------------------------------|-----|-----|------|--|--|--|

| Signal                       | Symbol | Parameter                     | Min | Max | Unit |  |  |  |

| CLKP/N, DnP/N                | SGD    | Input pulse rejection for DSI | -   | 300 | ∨ps  |  |  |  |

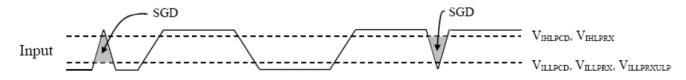

High Speed Mode

| Parameter                                                      | Symbol                   | Condition                       | S   | pecificatio | n   | Unit |

|----------------------------------------------------------------|--------------------------|---------------------------------|-----|-------------|-----|------|

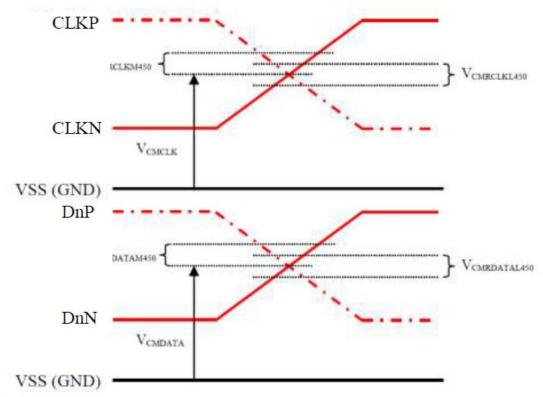

| Input Common Mode Voltage for Clock                            | V <sub>CMCLK</sub>       | CLKP/N<br>Note 2, Note 3        | 70  | -           | 330 | mV   |

| Input Common Mode Voltage for Data                             | V <sub>CMDATA</sub>      | DnP/N<br>Note 2, Note 3, Note 5 | 70  | -           | 330 | mV   |

| Common Mode Ripple for Clock Equal or Less<br>than 450MHz      | V <sub>CMRCLKL450</sub>  | CLKP/N<br>Note 4                | -50 | -           | 50  | mV   |

| Common Mode Ripple for Data Equal or Less<br>than 450MHz       | V <sub>CMRDATAL450</sub> | DnP/N<br>Note 4, Note 5         | -50 | -           | 50  | mV   |

| Common Mode Ripple for Clock More than 450MHz (peak sine wave) | V <sub>CMRCLKM450</sub>  | CLKP/N                          | -   | -           | 100 | mV   |

| Common Mode Ripple for Data More than 450MHz (peak sine wave)  | V <sub>CMRDATAM450</sub> | DnP/N<br>Note 5                 | -   | -           | 100 | mV   |

| Differential Input Low Level Threshold Voltage for Clock       | V <sub>THLCLK</sub>      | CLKP/N                          | -70 | -           | -   | mV   |

| Differential Input Low Level Threshold Voltage for Data        | V <sub>THLDATA</sub>     | DnP/N<br>Note 5                 | -70 | -           | -   | mV   |

| Differential Input High Level Threshold Voltage for Clock      | V <sub>THHCLK+</sub>     | CLKP/N                          | -   | -           | 70  | mV   |

| Differential Input High Level Threshold Voltage for Data       | V <sub>THHDATA</sub> +   | DnP/N<br>Note 5                 | -   | -           | 70  | mV   |

| Single-ended Input Low Voltage                                 | V <sub>ILHS</sub>        | CLKP/N, DnP/N<br>Note 3, Note 5 | -40 | -           | -   | mV   |

| Single-ended Input High Voltage                                | V <sub>IHHS</sub>        | CLKP/N, DnP/N<br>Note 3, Note 5 | -   | -           | 460 | mV   |

| Differential Termination Resistor                              | R <sub>TERM</sub>        | CLKP/N, DnP/N<br>Note 5         | 80  | 100         | 125 | Ω    |

| Single-ended Threshold Voltage for<br>Termination Enable       | V <sub>TERM-EN</sub>     | CLKP/N, DnP/N<br>Note 5         | -   | -           | 450 | mV   |

| Termination Capacitor                                          | $C_{TERM}$               | CLKP/N, DnP/N<br>Note 5, Note 6 | -   | -           | 60  | pF   |

Note: n = 0, 1, 2 and 3

## **7.AC Characteristics**

#### 7.1. DSI Interface Timing Characteristics

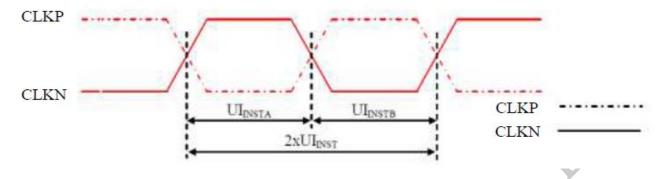

#### 7.1.1 High Speed Mode – Clock Channel Timing

| Signal | Symbol                                               | Parameter               | Min    | Max  | Unit |

|--------|------------------------------------------------------|-------------------------|--------|------|------|

| CLKP/N | 2xUI <sub>INST</sub>                                 | Double UI instantaneous | Note 2 | 25   | ns   |

| CLKP/N | UI <sub>INSTA</sub> ,UI <sub>INSTB</sub><br>(Note 1) | UI instantaneous Half   | Note 2 | 12.5 | ns   |

#### Notes:

#### 1. UI = UIINSTA = UIINSTB

| Data type                                                   | Two Lanes<br>speed | Three Lanes speed | Four Lanes<br>speed |

|-------------------------------------------------------------|--------------------|-------------------|---------------------|

| Data Type = 00 1110 (0Eh), RGB 565, 16 UI per Pixel         | 566 Mbps           | 466 Mbps          | 366 Mbps            |

| Data Type = 01 1110 (1Eh), RGB 666, 18 UI per Pixel         | 637 Mbps           | 525 Mbps          | 412 Mbps            |

| Data Type = 10 1110 (2Eh), RGB 666 Loosely, 24 UI per Pixel | 850 Mbps           | 700 Mbps          | 550 Mbps            |

| Data Type = 11 1110 (3Eh), RGB 888, 24 UI per Pixel         | 850 Mbps           | 700 Mbps          | 550 Mbps            |

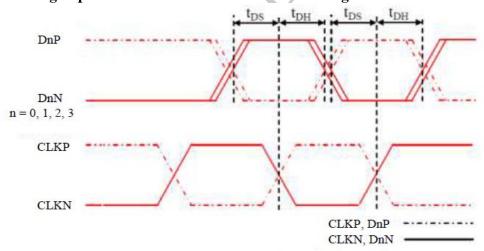

#### 7.1.2 High Speed Mode – Data Clock Channel Timing

| Signal Symbol     |                 | Parameter                | Min     | Max |

|-------------------|-----------------|--------------------------|---------|-----|

| DnP/N , n=0 and 1 | t <sub>DS</sub> | Data to Clock Setup time | 0.15xUI | 1   |

|                   | t <sub>DH</sub> | Clock to Data Hold Time  | 0.15xUI | 1   |

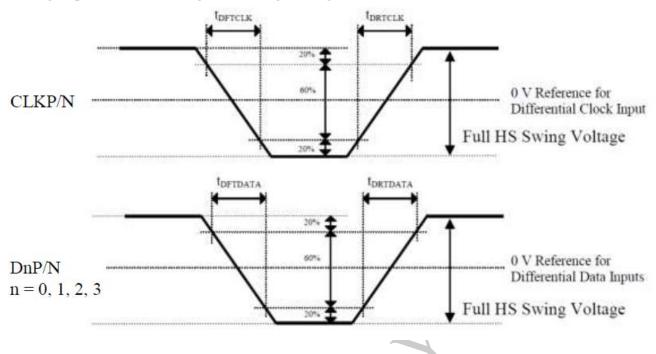

#### 7.1.3 High Speed Mode – Rising and Falling Timings

Table 41: Rise and Fall Timings on Clock and Data Channels

| B                                 | 0                    | 0 1141    | Specification |     |        |  |  |

|-----------------------------------|----------------------|-----------|---------------|-----|--------|--|--|

| Parameter                         | Symbol               | Condition | Min           | Тур | Max    |  |  |

| Differential Rise Time for Clock  |                      | CLVD/N    | 150 00        |     | 0.3UI  |  |  |

| Differential Rise Time for Clock  | t <sub>DRTCLK</sub>  | CLKP/N    | 150 ps        | -   | (Note) |  |  |

| Differential Disa Time for Date   | t <sub>DRTDATA</sub> | DnP/N     | 150 ps        | -   | 0.3UI  |  |  |

| Differential Rise Time for Data   |                      | n=0 and 1 |               |     | (Note) |  |  |

| Differential Fall Time for Olarly |                      | 011/0/11  | 450           |     | 0.3UI  |  |  |

| Differential Fall Time for Clock  | t <sub>DFTCLK</sub>  | CLKP/N    | 150 ps        | -   | (Note) |  |  |

| Differential Fall Time for Date   |                      | DnP/N     | 150           |     | 0.3UI  |  |  |

| Differential Fall Time for Data   | t <sub>DFTDATA</sub> | n=0 and 1 | 150 ps        | -   | (Note) |  |  |

**Note:** The display module has to meet timing requirements, which are defined for the transmitter (MCU) on MIPI D-Phy standard.

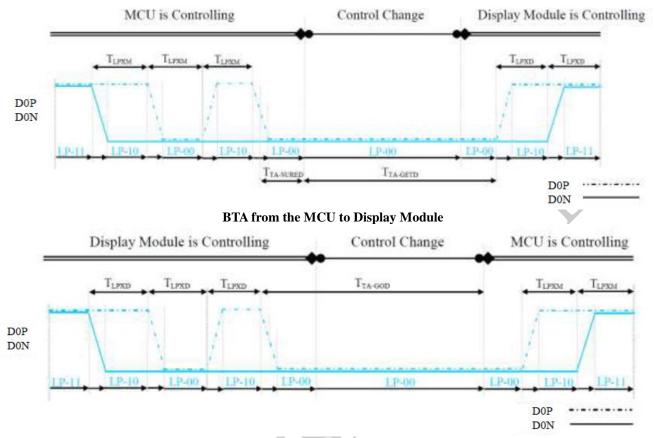

#### 7.1.4 Low Power Mode – Bus Turn Around

BTA from Display Module to the MCU

| Signal | Symbol                | Description                                                                     |                   | Max                 | Unit |

|--------|-----------------------|---------------------------------------------------------------------------------|-------------------|---------------------|------|

| D0P/N  | T <sub>LPXM</sub>     | Length of LP-00, LP-01, LP-10 or LP-11 periods  MCU → Display Module (ILI9881C) | 50                | 75                  | ns   |

| D0P/N  | T <sub>LPXD</sub>     | Length of LP-00, LP-01, LP-10 or LP-11 periods  Display Module (ILI9881C) → MCU |                   | 75                  | ns   |

| D0P/N  | T <sub>TA-SURED</sub> | Time-out before the Display Module (ILI9881C) starts driving                    | T <sub>LPXD</sub> | 2xT <sub>LPXD</sub> | ns   |

| Signal | Symbol               | Description                                        |                     | Unit |

|--------|----------------------|----------------------------------------------------|---------------------|------|

| D0P/N  | T <sub>TA-GETD</sub> | Time to drive LP-00 by Display Module (ILI9881C)   | 5xT <sub>LPXD</sub> | ns   |

| D0P/N  | T <sub>TA-GOD</sub>  | Time to drive LP-00 after turnaround request - MCU | 4xT <sub>LPXD</sub> | ns   |

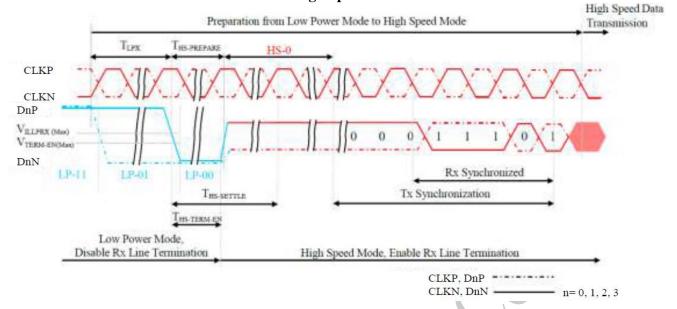

#### 7.1.5 Data Lanes from Low Power Mode to High Speed Mode

| Signal             | Symbol                  | Description                                                                             | Min     | Max     | Unit |

|--------------------|-------------------------|-----------------------------------------------------------------------------------------|---------|---------|------|

| DnP/N, n = 0 and 1 | T <sub>LPX</sub>        | Length of any Low Power State Period                                                    | 50      | -       | ns   |

| DnP/N, n = 0 and 1 | T <sub>HS-PREPARE</sub> | Time to drive LP-00 to prepare for HS Transmission                                      | 40+4xUI | 85+6xUI | ns   |

| DnP/N, n = 0 and 1 | T <sub>HS-TERM-EN</sub> | Time to enable Data Lane Receiver line termination measured from when Dn crosses VILMAX | -       | 35+4xUI | ns   |

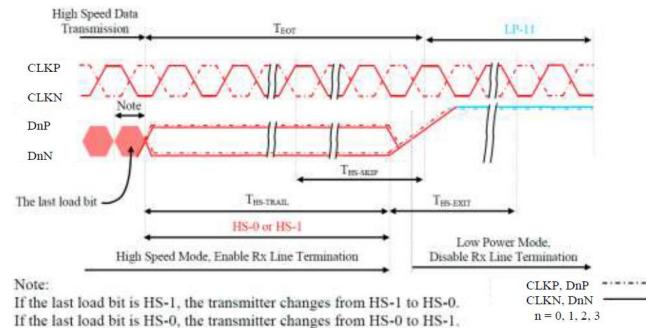

#### 7.1.6 Data Lanes from High Speed Mode to Low Power Mode

| Signal             | Symbol               | Description                                                              | Min | Max     | Unit |

|--------------------|----------------------|--------------------------------------------------------------------------|-----|---------|------|

| DnP/N, n = 0 and 1 | T <sub>HS-SKIP</sub> | Time-Out at Display Module (ILI9881C) to ignore transition period of EoT | 40  | 55+4xUI | ns   |

| DnP/N, n = 0 and 1 | T <sub>HS-EXIT</sub> | Time to driver LP-11 after HS burst                                      | 100 | -       | ns   |

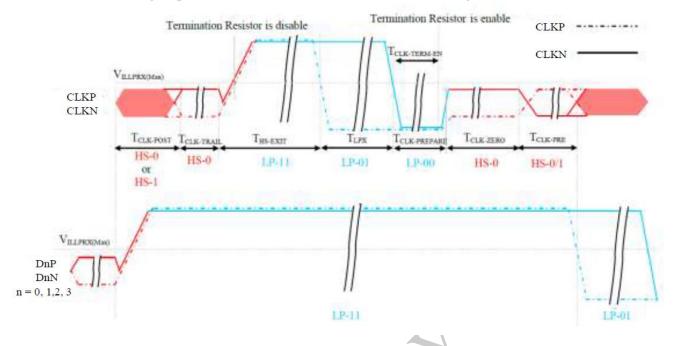

#### 7.1.7 Clock Lanes High Speed Mode to/from Low Power Mode Timing

| Signal | Symbol                                           | Description                                                                                                          | Min      | Max | Unit |

|--------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------|-----|------|

| CLKP/N | T <sub>CLK-POST</sub>                            | Time that the MCU shall continue sending HS clock after the last associated Data Lanes has transitioned to LP mode   | 60+52xUI | -   | ns   |

| CLKP/N | T <sub>CLK-TRAIL</sub>                           | Time to drive HS differential state after last payload clock bit of a HS transmission burst                          |          | -   | ns   |

| CLKP/N | T <sub>HS-EXIT</sub>                             | Time to drive LP-11 after HS burst                                                                                   | 100      | -   | ns   |

| CLKP/N | T <sub>CLK-PREPARE</sub>                         | Time to drive LP-00 to prepare for HS transmission                                                                   | 38       | 95  | ns   |

| CLKP/N | T <sub>CLK-TERM-EN</sub>                         | Time-out at Clock Lane to enable HS termination                                                                      | •        | 38  | ns   |

| CLKP/N | T <sub>CLK-PREPARE</sub> + T <sub>CLK-ZERO</sub> | Minimum lead HS-0 drive period before starting Clock                                                                 | 300      | -   | ns   |

| CLKP/N | T <sub>CLK-PRE</sub>                             | Time that the HS clock shall be driven prior to any associated Data Lane beginning the transition from LP to HS mode | 8xUI     | -   | ns   |

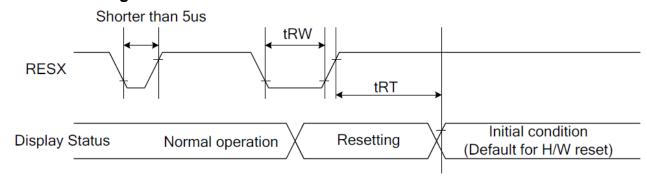

#### 7.2. Reset Timing

| Signal | Symbol       | Parameter            | Min                | Max           | Unit |

|--------|--------------|----------------------|--------------------|---------------|------|

| RESX   | tRW          | Reset pulse duration | 10                 |               | us   |

|        | +DT          | Ponet concel         |                    | 5 (Note 1, 5) | mo   |

| tRT    | Reset cancel |                      | 120 (Note 1, 6, 7) | ms            |      |

#### Notes:

- 1. The reset cancel includes also required time for loading ID bytes, VCOM setting and other settings from NVM (or similar device) to registers. This loading is done every time when there is HW reset cancel time (tRT) within 5 ms after a rising edge of RESX.

- 2. Spike due to an electrostatic discharge on RESX line does not cause irregular system reset according to the table below:

| RESX Pulse           | Action         |

|----------------------|----------------|

| Shorter than 5us     | Reset Rejected |

| Longer than 10us     | Reset          |

| Between 5us and 10us | Reset starts   |

- 3. During the Resetting period, the display will be blanked (The display is entering blanking sequence, which maximum time is 120 ms, when Reset Starts in Sleep Out –mode. The display remains the blank state in Sleep In –mode.) and then return to Default condition for Hardware Reset.

- 4. Spike Rejection also applies during a valid reset pulse as shown below:

- 5. When Reset applied during Sleep In Mode.

- 6. When Reset applied during Sleep Out Mode.

- 7. It is necessary to wait 5msec after releasing RESX before sending commands. Also Sleep Out command cannot be sent for 120msec.

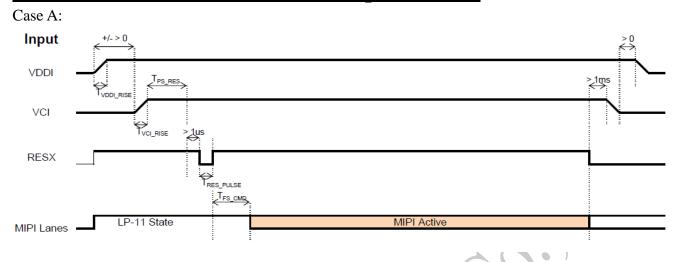

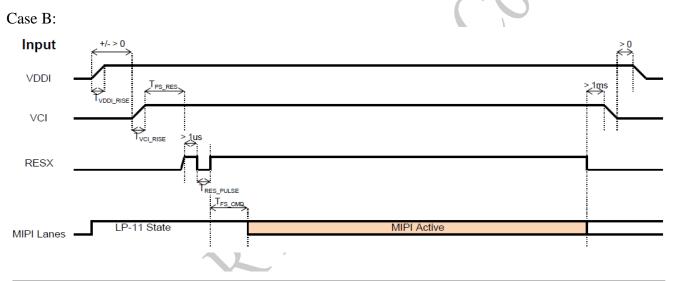

## **8.Power ON/OFF Sequence**

| Symbol                  | Characteristics           | Min. | Тур. | Max. | Units |

|-------------------------|---------------------------|------|------|------|-------|

| T <sub>VDDI_RISE</sub>  | VDDI Rise time            | 10   | -    | -    | us    |

| т                       | Case A: VCI Rise time     | 130  |      |      | ПС    |

| T <sub>VCI_RISE</sub> - | Case B: VCI Rise time     | 40   | -    | -    | us    |

| T <sub>PS_RES</sub>     | VDDI/VCI on to Reset high | 5    | -    | -    | ms    |

| T <sub>RES_PULSE</sub>  | Reset low pulse time      | 10   | -    | -    | us    |

| T <sub>FS_CMD</sub>     | Reset to first command    | 10   | -    | -    | ms    |

## 9. Optical Characteristics

| Item           |      | Symbol | Condition.                 | Min   | Тур.  | Max.  | Unit              | Remark            |

|----------------|------|--------|----------------------------|-------|-------|-------|-------------------|-------------------|

| Response time  |      | Tr     | θ=0° \ Φ=0°                | -     | 10    | 15    | .ms               | Note 2 F          |

| i tooponee un  |      | Tf     |                            | -     | 20    | 25    | .ms               | Note 3,5          |

| Contrast ratio |      | CR     | At optimized viewing angle | 640   | 800   | 1     | -                 | Note 4,5          |

| Color Whit     |      | Wx     | θ=0°、Φ=0                   | 0.283 | 0.303 | 0.323 |                   | Note 2,6,7        |

| Chromaticity   | е    | Wy     |                            | 0.303 | 0.323 | 0.343 | X                 | Note 2,6,7        |

|                | Hor. | ΘR     |                            | -     | 80    | -     |                   | 2                 |

| Viowing angle  |      | ΘL     | CR≧10                      | -     | 80    | -     | Deg.              | Note 1            |

| Viewing angle  |      | ΦТ     | 511_15                     | -     | 80    |       | Sog.              | Note 1            |

|                | Ver. | ΦВ     |                            | -     | 80    | 2     |                   |                   |

| Brightness     |      | -      | -                          | 200   | 250   | -     | cd/m <sup>2</sup> | Center of display |

| Uniformity     |      | (U)    | -                          | 75    | -     | -     | %                 | Note 5            |

Ta=25±2°C

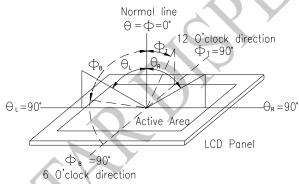

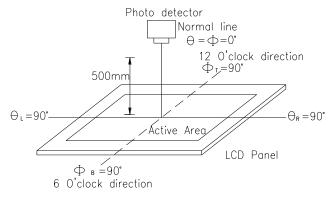

Note 1: Definition of viewing angle range

Fig. 9.1. Definition of viewing angle

Note 2: Test equipment setup:

After stabilizing and leaving the panel alone at a driven temperature for 10 minutes, the measurement should be executed. Measurement should be executed in a stable, windless, and dark room. Optical specifications are measured by Topcon BM-7or BM-5 luminance meter 1.0° field of view at a distance of 50cm and normal direction.

Fig. 9.2. Optical measurement system setup

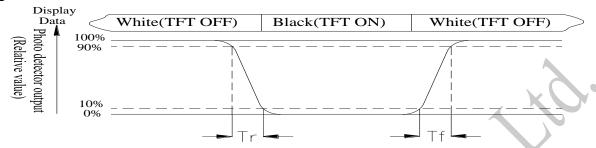

#### Note 3: Definition of Response time:

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time, Tr, is the time between photo detector output intensity changed from 90%to 10%. And fall time, Tf, is the time between photo detector output intensity changed from 10%to 90%

Note 4: Definition of contrast ratio:

The contrast ratio is defined as the following expression.

Contrast ratio (CR) = Luminance measured when LCD on the "White" state

Luminance measured when LCD on the "Black" state

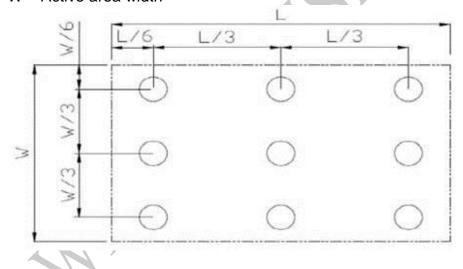

#### Note 5: Definition of Luminance Uniformity

Active area is divided into 9 measuring areas (reference the picture in below). Every measuring point is placed at the center of each measuring area.

Luminance Uniformity (U) = Lmin/Lmax x100%

L = Active area length

W = Active area width

Fig 9.3. Definition of uniformity

Note 6: Definition of color chromaticity (CIE 1931) Color coordinates measured at the center point of LCD

Note 7: Measured at the center area of the panel when all the input terminals of LCD panel are electrically opened.

# 10.1nterface 10.1. LCM PIN Definition

| Pin   | Symbol | Function                                                                                                                                                      | Remark |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1     | NC     | No connection                                                                                                                                                 |        |

| 2     | NC     | No connection                                                                                                                                                 |        |

| 3     | NC     | No connection                                                                                                                                                 |        |

| 4     | NC     | No connection                                                                                                                                                 | 7.     |

| 5     | NC     | No connection                                                                                                                                                 |        |

| 6     | NC     | No connection                                                                                                                                                 |        |

| 7     | NC     | No connection                                                                                                                                                 |        |

| 8     | NC     | No connection                                                                                                                                                 |        |

| 9     | NC     | No connection                                                                                                                                                 |        |

| 10-11 | VCI    | Power supply for analog circuits. Connect to an external power supply of 2.5V to 3.6V                                                                         |        |

| 12-13 | NC     | No connection                                                                                                                                                 |        |

| 14    | RESET  | The external reset input Initializes the chip with a low input. Be sure to execute a power-on reset after supplying power. Fix to VDDI level when not in use. |        |

| 15    | TE     | Tearing effect output pin. Leave the pin open when not in use.                                                                                                |        |

| 16    | NC     | No connection                                                                                                                                                 |        |

| 17-18 | GND    | Power ground                                                                                                                                                  |        |

| 19-20 | IOVCC  | Power supply for analog circuits. Connect to an external power supply of 1.65V to 3.6V                                                                        |        |

| 21    | GND    | Power ground                                                                                                                                                  |        |

| 22    | D3P    | MIPI DSI differential data pair. (Data lane 3)                                                                                                                |        |

| 23    | D3N    | Will I Bol differential data pail. (Bata faile 6)                                                                                                             |        |

| 24    | GND    | Power ground                                                                                                                                                  |        |

| 25    | D2P    | MIPI DSI differential data pair. (Data lane 2)                                                                                                                |        |

| 26    | D2N    | MIPI DSI dillerential data pair. (Data lane 2)                                                                                                                |        |

| 27    | GND    | Power ground                                                                                                                                                  |        |

| 28    | CLKP   | MIPI DSI differential clock pair                                                                                                                              |        |

| 29    | CLKN   | Will I Dol alliototiliai Gook pali                                                                                                                            |        |

| 30    | GND    | Power ground                                                                                                                                                  |        |

| 31    | D1P    | MIPI DSI differential data pair. (Data lane 1)                                                                                                                |        |

| 32    | D1N   |                                                |  |

|-------|-------|------------------------------------------------|--|

| 33    | GND   | Power ground                                   |  |

| 34    | D0P   | MIDI DSI differential data pair (Data lane 0)  |  |

| 35    | D0N   | MIPI DSI differential data pair. (Data lane 0) |  |

| 36-37 | GND   | Power ground                                   |  |

| 38    | LED+  | Power for LED backlight anode                  |  |

| 39    | LED1- | Power for LED1 backlight cathode               |  |

| 40    | LED2- | Power for LED2 backlight cathode               |  |

#### 10.2. CTP PIN Definition

| Pin | Symbol | Function                       | Remark |

|-----|--------|--------------------------------|--------|

| 1   | SDA    | I2C data input and output      |        |

| 2   | SCL    | I2C clock input                |        |

| 3   | RST    | External Reset, Low is active  |        |

| 4   | INT    | External interrupt to the host |        |

| 5   | VDD    | Power Supply: +3.3V            |        |

| 6   | GND    | Ground for analog circuit      |        |

## 11.Reliability

Content of Reliability Test (Wide temperature, -20°C ~70°C)

| Environmental Test                               |                                                                                                                                             |                                                                                                                             |      |  |  |  |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|--|--|--|

| Test Item                                        | Content of Test                                                                                                                             | Test Condition                                                                                                              | Note |  |  |  |

| High Temperature storage Low Temperature storage | Endurance test applying the high storage temperature for a long time.  Endurance test applying the low storage temperature for a long time. | 80°C<br>200hrs<br>-30°C<br>200hrs                                                                                           | 2    |  |  |  |

| High Temperature<br>Operation                    | Endurance test applying the electric stress (Voltage & Current) and the thermal stress to the element for a long time.                      | 70°C<br>200hrs                                                                                                              |      |  |  |  |

| Low Temperature<br>Operation                     | Endurance test applying the electric stress under low temperature for a long time.                                                          | -20℃<br>200hrs                                                                                                              | 1    |  |  |  |

| High Temperature/<br>Humidity Operation          | The module should be allowed to stand at 60°C,90%RH max                                                                                     | 60℃,90%RH<br>96hrs                                                                                                          | 1,2  |  |  |  |

| Thermal shock resistance                         | The sample should be allowed stand the following 10 cycles of operation  -20°C 25°C 70°C  30min 5min 30min 1 cycle                          | -20°ℂ/70°ℂ<br>10 cycles                                                                                                     |      |  |  |  |

| Vibration test                                   | Endurance test applying the vibration during transportation and using.                                                                      | Total fixed amplitude: 1.5mm Vibration Frequency: 10~55Hz One cycle 60 seconds to 3 directions of X,Y,Z for Each 15 minutes | 3    |  |  |  |

| Static electricity test                          | Endurance test applying the electric stress to the terminal.                                                                                | VS=±600V(contact),<br>±800v(air),<br>RS=330Ω<br>CS=150pF<br>10 times                                                        |      |  |  |  |

Note1: No dew condensation to be observed.

Note2: The function test shall be conducted after 4 hours storage at the normal

Temperature and humidity after remove from the test chamber.

Note3: The packing have to including into the vibration testing.

## **12.Touch Panel Information**

#### 12.1. I2C Communication

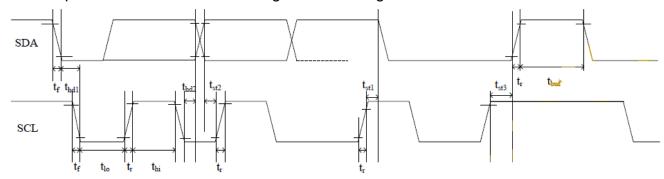

GT928 provides standard I2C interface for communication. In the system, GT928 always works in slave mode, all communications are initiated by master, and the baud rate can be up to 400K bps. The definition of I2C timing is as following:

Test condition1: 1.8V communication interface, 400Kbps, pull up resistor is 2K ohm

| Parameter                          | Symbol | Min. | Max. | Unit |

|------------------------------------|--------|------|------|------|

| SCL low period                     | Tlo    | 0.9  | -    | us   |

| SCL high period                    | Thi    | 0.8  | -    | us   |

| SCL setup time for START condition | tst1   | 0.4  | -    | us   |

| SCL setup time for STOP condition  | tst3   | 0.4  | -    | us   |

| SCL hold time for START condition  | thd1   | 0.3  | -    | us   |

| SDA setup time                     | tst2   | 0.4  | -    | us   |

| SDA hold time                      | thd2   | 0.4  | -    | us   |

Test condition2: 3.3V communication interface, 400Kbps, pull up resistor is 2K ohm

| Parameter                          | Symbol | Min. | Max. | Unit |

|------------------------------------|--------|------|------|------|

| SCL low period                     | Tlo    | 0.9  | -    | us   |

| SCL high period                    | Thi    | 0.8  | -    | us   |

| SCL setup time for START condition | tst1   | 0.4  | -    | us   |

| SCL setup time for STOP condition  | tst3   | 0.4  | -    | us   |

| SCL hold time for START condition  | thd1   | 0.3  | -    | us   |

| SDA setup time                     | tst2   | 0.4  | -    | us   |

| SDA hold time                      | thd2   | 0.4  | -    | us   |

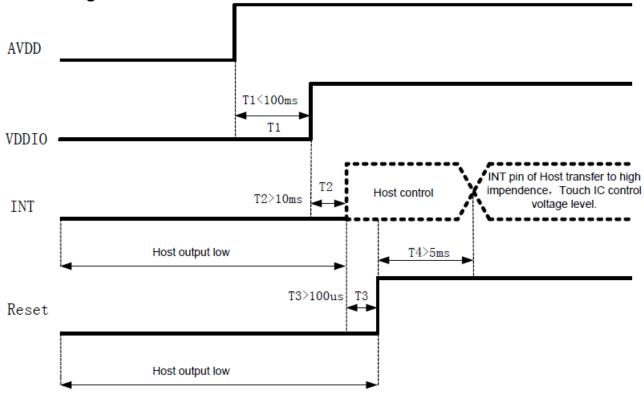

GT928 has 2 sets of slave address 0xBA/0xBB & 0x28/29. Master can control Reset & INT pin to configure the slave address in power on initial state like following:

Power on diagram:

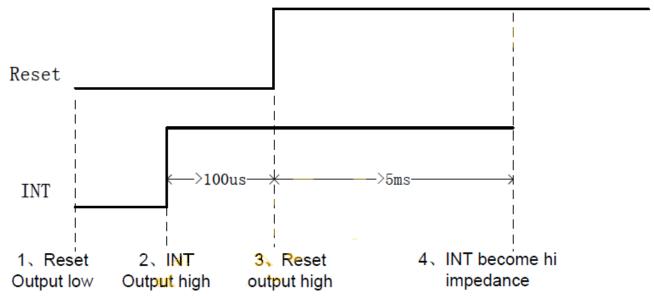

#### Timing of setting slave address to 0x28/0x29:

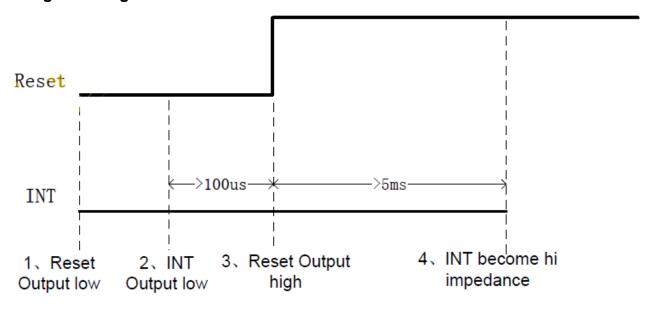

#### Timing of setting slave address to 0xBA/0xBB:

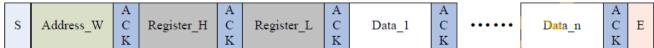

#### a) Data Transmission

(eg. slave address is 0xBA/0xBB)

Communication is always initiated by master, A high-to-low transition of SDA with SCL high is a start condition.

All addressing signal are serially transmitted to and from on bus in 8-bit word. GT928 sends a "0" to acknowledge when the addressing word is 0xBA/BB( or 0x28/0x29 ). This happens during the ninth clock cycle. If the slave address is not matched, GT928 will stay in idle state. The data words are serially transmitted to and from in 9-bit information: 8-bit data + 1-bit ACK or NACK sent by GT928. Data changes during SCL low periods and keep valid during SCL high.

A low-to-high transition of SDA with SCL high is a stop condition.

#### b) Write Data to GT928

(eg. slave address is 0xBA/0xBB)

#### Write operations

Please check the above figure, master start the communication first, and then sends device address 0XBA preparing for a write operation.

After receiving ACK from GT928, master sends out 16-bit register address, and then the data word in 8-bit, which is going to be wrote into GT928.

The address pointer of GT928 will automatically increase one after one byte writing, so master can sequentially write in one operation. When operation finished, master stop the communication.

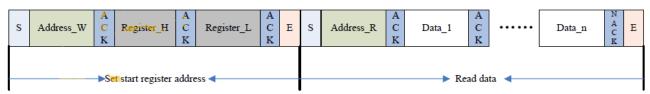

#### c) Read Data from GT928

(eg. slave address is 0xBA/0xBB)

#### **Read operation**

Please check the above figure, master start the communication first, and then sends device address 0xBA for a write operation.

After receiving ACK from GT928, master sends out 16-bit register address, to set the address pointer of GT913. After receiving ACK, master produce start signal once again and send device address 0xBB, then read data word from GT928 in 8-bit.

GT928 also supports sequential read operation, and the default setting is sequential read mode. Master shall send out ACK after every byte reading successfully but NACK after the last one. Then sends stop signal to finish the communication

## **13.Contour Drawing**

#### **LCM Sample Estimate Feedback Sheet**

| Module       | Number:                    |        | Pa            | ge: 1    |

|--------------|----------------------------|--------|---------------|----------|

| 1 ⋅ <u>P</u> | anel Specification:        |        |               |          |

| 1.           | Panel Type:                | □ Pass | □ NG ,        |          |

| 2.           | View Direction:            | □ Pass | □ NG ,        |          |

| 3.           | Numbers of Dots:           | □ Pass | □ NG ,        |          |

| 4.           | View Area:                 | □ Pass | □ NG ,        |          |

| 5.           | Active Area:               | □ Pass | □ NG ,        |          |

| 6.           | Operating                  | □ Pass | □ NG ,        | <b>J</b> |

| 7.           | Storage Temperature :      | □ Pass | □ NG ,        |          |

| 8.           | Others:                    |        | Y             | _        |

| 2 · <u>N</u> | <u>lechanical</u>          |        |               |          |

| 1.           | PCB Size :                 | □ Pass | □ NG ,        |          |

| 2.           | Frame Size :               | □ Pass | □ NG ,        |          |

| 3.           | Material of Frame:         | □ Pass | □ NG ,        |          |

| 4.           | Connector Position:        | □ Pass | □ NG ,        |          |

| 5.           | Fix Hole Position:         | □ Pass | □ NG ,        |          |

| 6.           | Backlight Position:        | □ Pass | □ NG ,        |          |

| 7.           | Thickness of PCB:          | □ Pass | л NG ,        |          |

| 8.           | Height of Frame to         | □ Pass | □ NG ,        |          |

| 9.           | Height of Module:          | □ Pass | □ NG ,        |          |

| 10.          | Others:                    | □ Pass | □ NG ,        |          |

| 3 ⋅ <u>R</u> | elative Hole Size :        |        |               |          |

| 1.           | Pitch of Connector:        | □ Pass | □ NG ,        |          |

| 2.           | Hole size of Connector:    | □ Pass | □ NG ,        |          |

| 3.           | Mounting Hole size:        | □ Pass | □ NG ,        |          |

| 4.           | Mounting Hole Type:        | □ Pass | □ NG ,        |          |

| 5.           | Others:                    | □ Pass | □ NG ,        |          |

| 4 √ <u>B</u> | acklight Specification :   |        |               |          |

| 1.           | B/L Type:                  | □ Pass | □ NG ,        |          |

| 2. l         | B/L Color:                 | □ Pass | □ NG ,        |          |

| 3. <u>l</u>  | B/L Driving Voltage (Refer |        | □ Pass □ NG , |          |

| 4.           | B/L Driving Current:       | □ Pass | □ NG ,        |          |

| 5. l         | Brightness of B/L:         |        | □ NG ,        |          |

| 6. l         | B/L Solder Method:         |        | □ NG ,        |          |

| 7.           | Others:                    | □ Pass | □ NG ,        |          |

### >> Go to page 2 <<

| Vinst | ar Module Number: _        |             | Page: 2   |

|-------|----------------------------|-------------|-----------|

| 5、    | Electronic Characteristics | of Module:  |           |

| 1.    | Input Voltage:             | □ Pass      | □ NG ,    |

| 2.    | Supply Current:            | □ Pass      | □ NG ,    |

| 3.    | Driving Voltage for LCD:   | □ Pass      | □ NG ,    |

| 4.    | Contrast for LCD:          | □ Pass      | □ NG ,    |

| 5.    | B/L Driving Method:        | □ Pass      | □ NG ,    |

| 6.    | Negative Voltage Output:   | □ Pass      | □ NG ,    |

| 7.    | Interface Function:        | □ Pass      | □ NG ,    |

| 8.    | LCD Uniformity:            | □ Pass      | □ NG ,    |

| 9.    | ESD test:                  | □ Pass      | □ NG ,    |

| 10.   | Others:                    | □ Pass      | □ NG ,    |

| 6     | Summary :                  | 4           |           |

| Sales | signature:                 | (0)         |           |

| lieto | mer Signature :            | $\lambda V$ | Date: / / |